SNOSD54 June 2017 LM339-MIL

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

封裝選項(xiàng)

機(jī)械數(shù)據(jù) (封裝 | 引腳)

- J|14

散熱焊盤(pán)機(jī)械數(shù)據(jù) (封裝 | 引腳)

訂購(gòu)信息

6 Specifications

6.1 Absolute Maximum Ratings

See (1)(2)| MIN | MAX | UNIT | |||

|---|---|---|---|---|---|

| Supply voltage, V+ | 36 | VDC | |||

| Differential input voltage(3) | 36 | ||||

| Input voltage | –0.3 | 36 | |||

| Input current (VIN ≤ 0.3 VDC)(4) | 50 | mA | |||

| Power dissipation(5) | PDIP | 1050 | mW | ||

| Cavity DIP | 1190 | ||||

| SOIC package | 760 | ||||

| Output short-circuit to GND(6) | Continuous | ||||

| Storage temperature, Tstg | −65 | 150 | °C | ||

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Refer to RETS139X for military specifications.

(3) Positive excursions of input voltage may exceed the power supply level. As long as the other voltage remains within the common-mode range, the comparator will provide a proper output state. The low input voltage state must not be less than −0.3 VDC (or 0.3 VDC below the magnitude of the negative power supply, if used) (at 25°C).

(4) This input current will only exist when the voltage at any of the input leads is driven negative. It is because of the collector-base junction of the input PNP transistors becoming forward biased and thereby acting as input diode clamps. In addition to this diode action, there is also lateral NPN parasitic transistor action on the IC chip. This transistor action can cause the output voltages of the comparators to go to the V+ voltage level (or to ground for a large overdrive) for the time duration that an input is driven negative. This is not destructive and normal output states will re-establish when the input voltage, which was negative, again returns to a value greater than −0.3 VDC (at 25°C).

(5) For operating at high temperatures, the device must be derated based on a 125°C maximum junction temperature and a thermal resistance of 95°C/W which applies for the device soldered in a printed circuit board, operating in a still air ambient. The low bias dissipation and the ON-OFF characteristic of the outputs keeps the chip dissipation very small (PD ≤ 100 mW), provided the output transistors are allowed to saturate.

(6) Short circuits from the output to V+ can cause excessive heating and eventual destruction. When considering short circuits to ground, the maximum output current is approximately 20 mA independent of the magnitude of V+.

6.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | ±600 | V |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)| MIN | MAX | UNIT | |

|---|---|---|---|

| Supply voltage, single | 2 | 36 | V |

| Supply voltage, dual | ±1 | ±18 | |

| Operating temperature | 0 | 70 | °C |

6.4 Thermal Information

| THERMAL METRIC(1) | LM339-MIL | UNIT | |||

|---|---|---|---|---|---|

| J (CDIP) | D (SOIC) | NFF (PDIP) | |||

| 14 PINS | 14 PINS | 14 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 97.8 | 94.3 | 82.3 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 52.6 | 52.4 | 79 | °C/W |

| RθJB | Junction-to-board thermal resistance | 87.5 | 48.8 | 62.1 | °C/W |

| ψJT | Junction-to-top characterization parameter | 43.9 | 14.2 | 50.9 | °C/W |

| ψJB | Junction-to-board characterization parameter | 80.3 | 48.5 | 62 | °C/W |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | 30.1 | — | — | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

6.5 Electrical Characteristics

(V+ = 5 VDC, TA = 25°C, unless otherwise stated)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|---|---|---|---|---|---|

| Input offset voltage | At output switch point, VO ? 1.4 VDC, RS = 0 Ω with V+ from 5 VDC to 30 VDC; and over the full input common-mode range (0 VDC to V+ −1.5 VDC), at 25°C. | 2 | 5 | mVDC | |

| At output switch point, VO ? 1.4 VDC, RS = 0 Ω with V+ from 5 VDC to 30 VDC; and over the full input common-mode range (0 VDC to V+ −1.5 VDC), at 25°C, 0°C ≤ TA ≤ 70°C | 9 | ||||

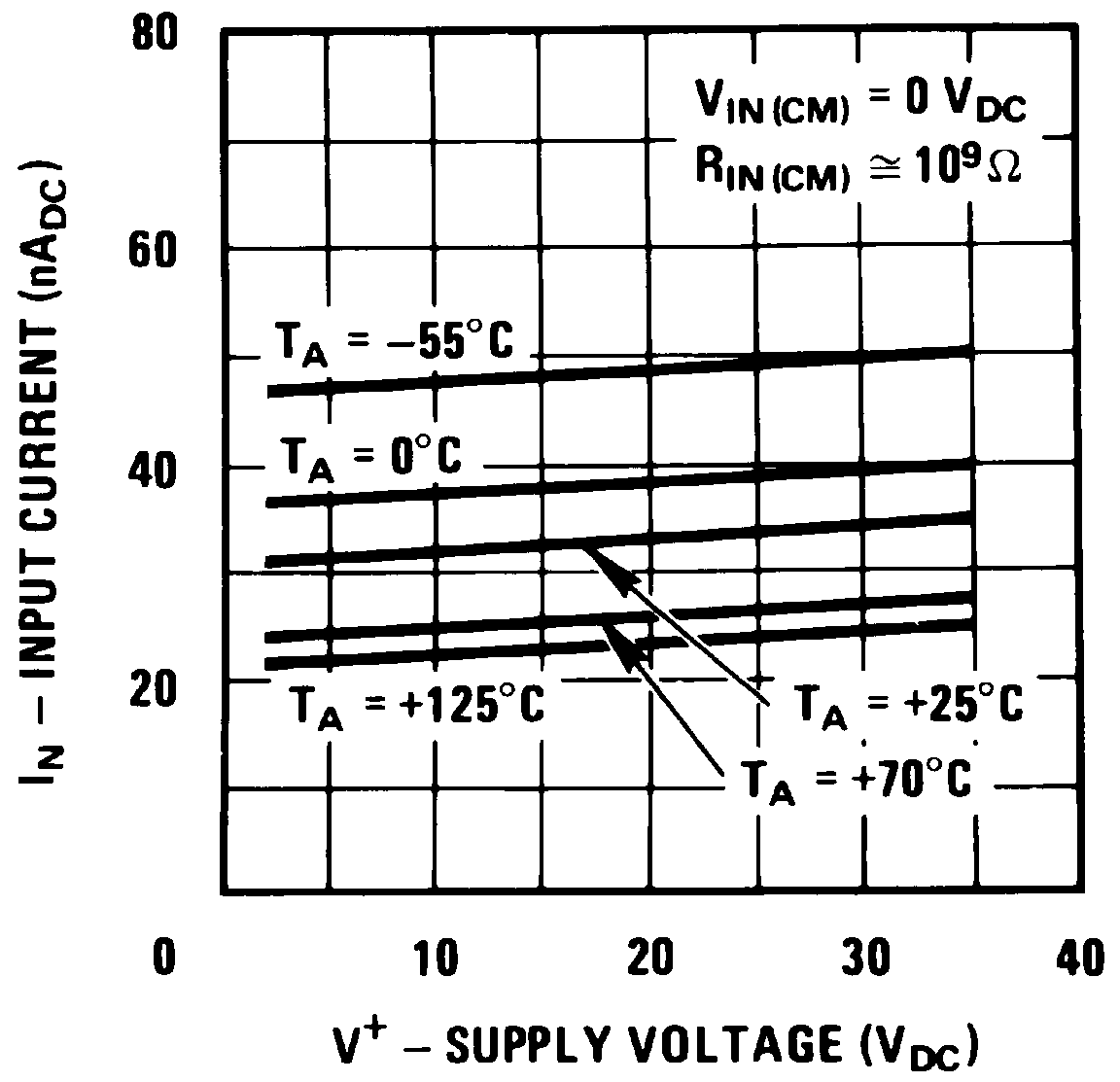

| Input bias current(1) | IIN(+) or IIN(−) with output in linear range, VCM = 0 V | 25 | 250 | nADC | |

| IIN(+) or IIN(−) with output in linear range, VCM = 0 V, 0°C ≤ TA ≤ 70°C | 400 | ||||

| Input offset current | IIN(+)− IIN(−), VCM = 0 V | 5 | 50 | nADC | |

| IIN(+)− IIN(−), VCM = 0 V, 0°C ≤ TA ≤ 70°C | 150 | ||||

| Input common-mode voltage range(2) | V+ = 30 VDC | 0 | V+ − 1.5 | VDC | |

| V+ = 30 VDC, 0°C ≤ TA ≤ 70°C | V+ – 2 | ||||

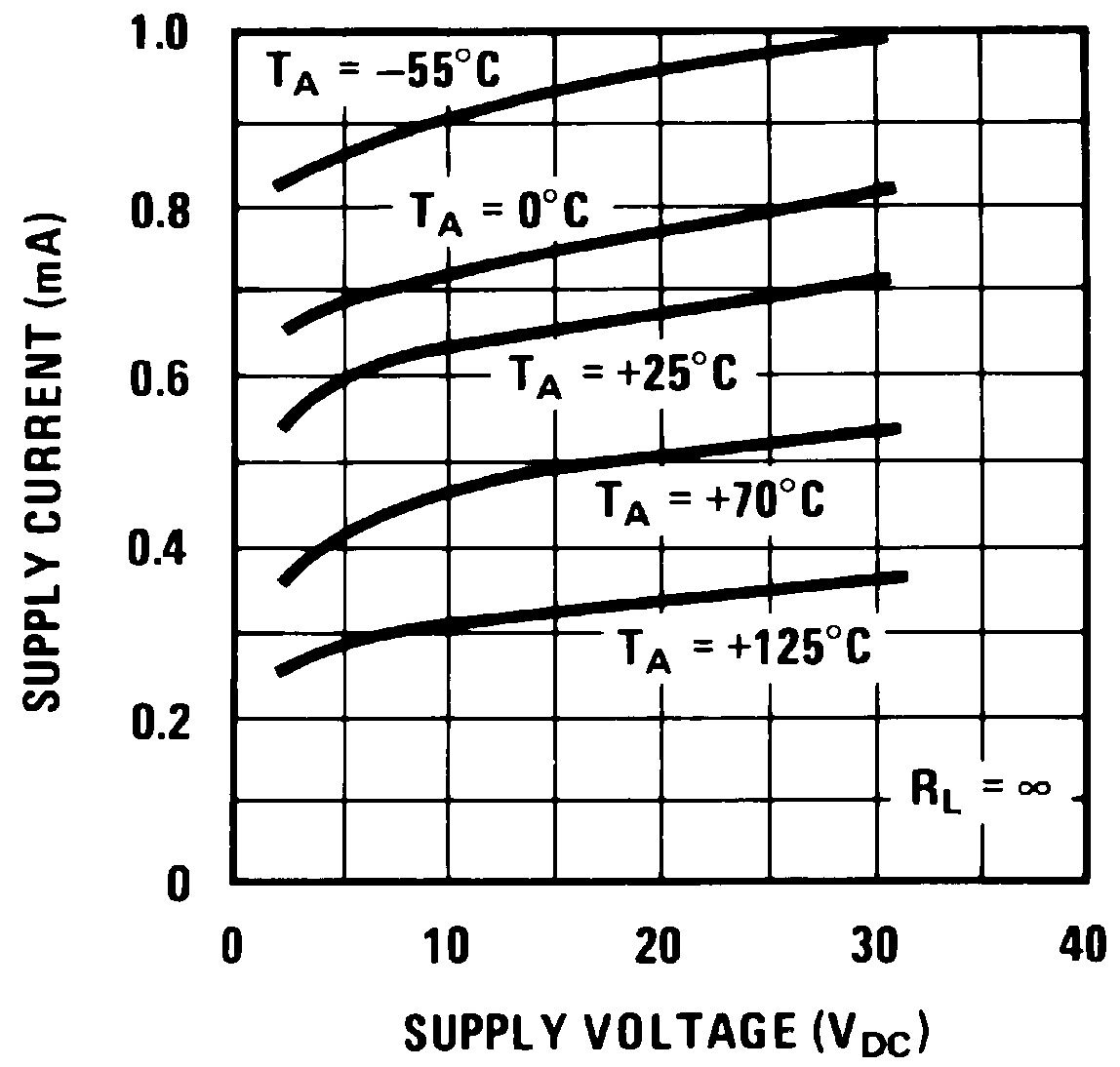

| Supply current | RL = ∞ on all comparators | 0.8 | 2 | mADC | |

| RL = ∞, V+ = 36 V | 1 | 2.5 | mADC | ||

| Voltage gain | RL ≥ 15 kΩ, V+ = 15 VDC, VO = 1 VDC to 11 VDC | 50 | 200 | V/mV | |

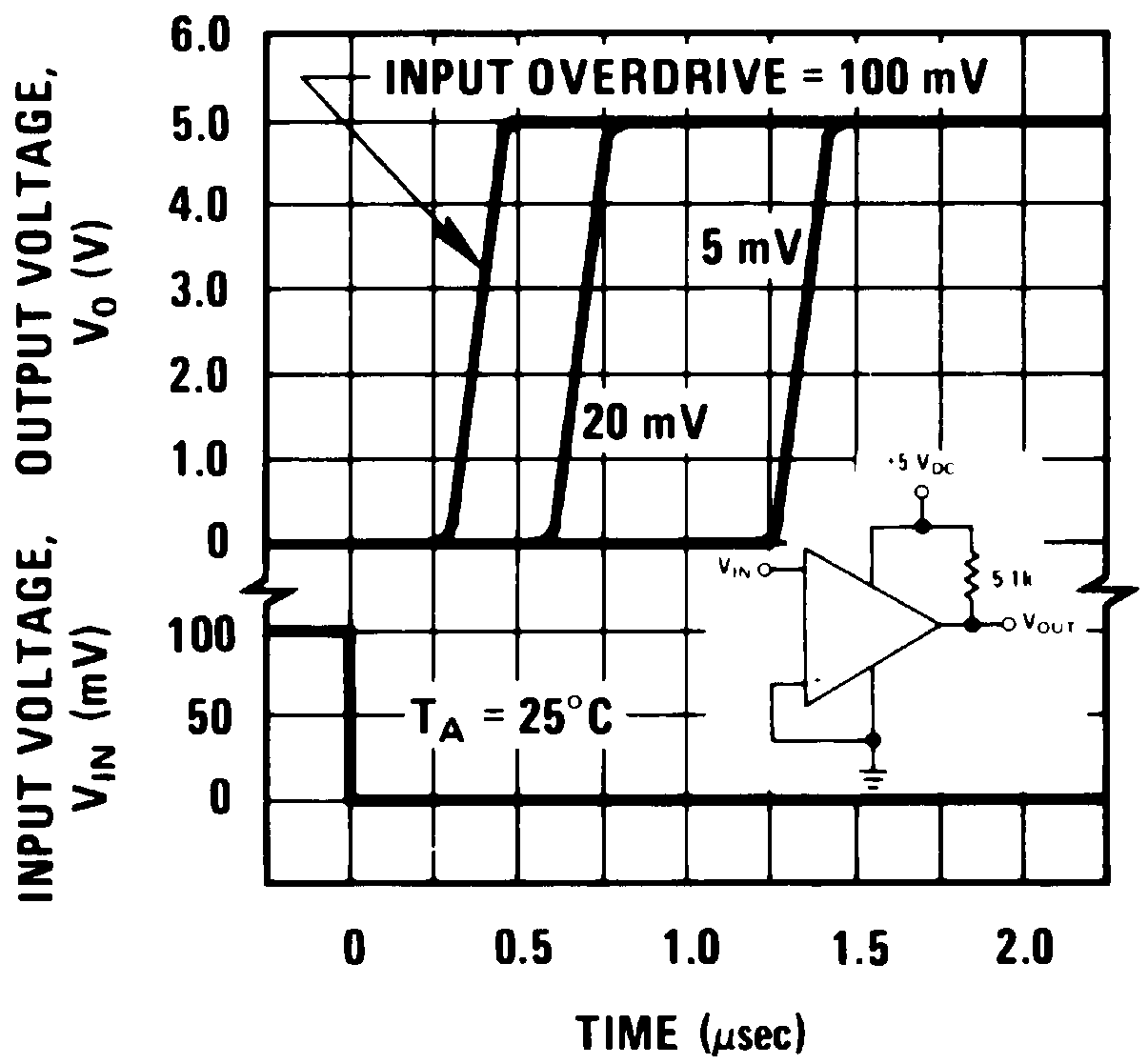

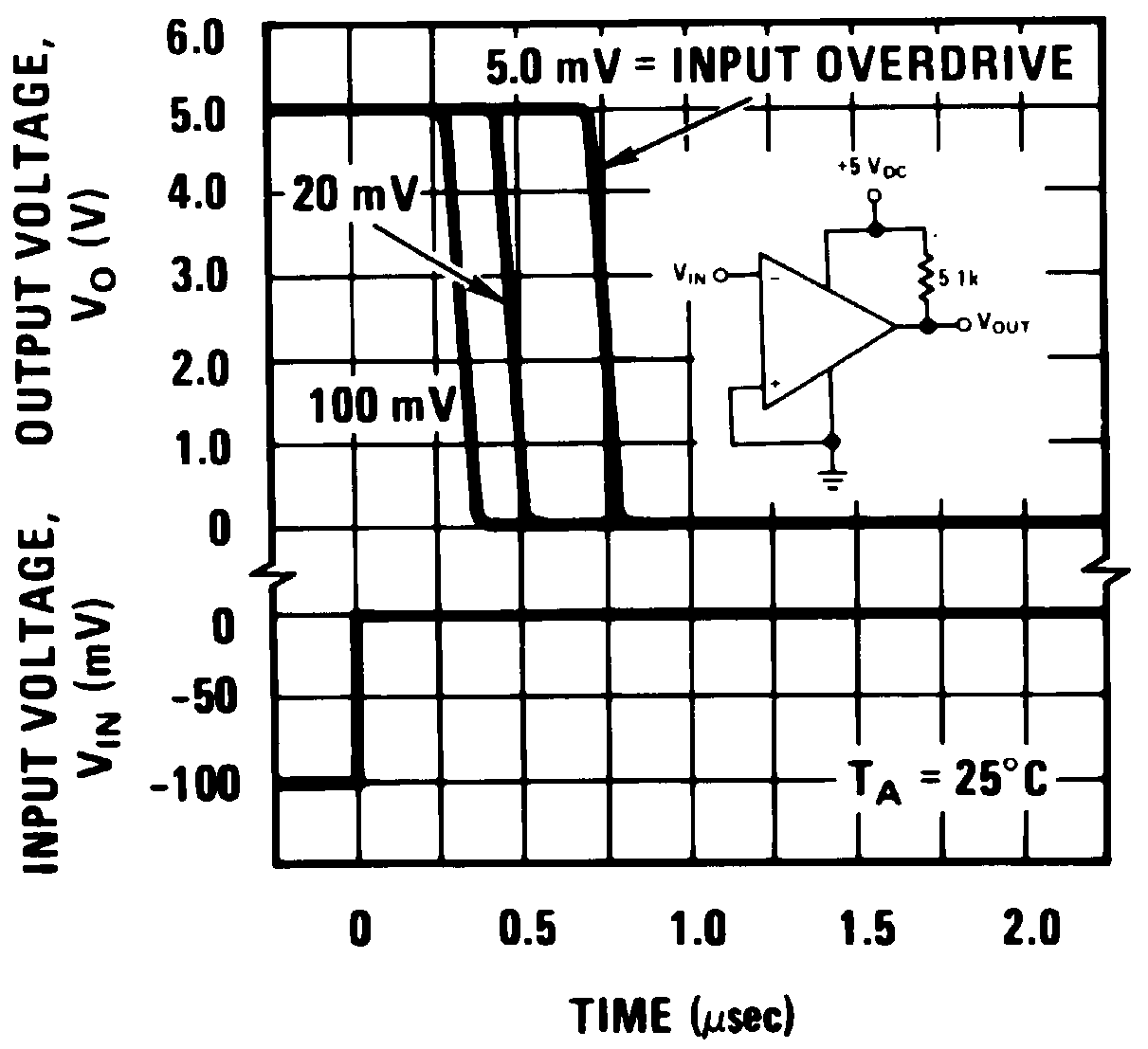

| Large signal response time | VIN = TTL logic swing, VREF = 1.4 VDC, VRL = 5 VDC, RL = 5.1 kΩ | 300 | ns | ||

| Response time(3) | VRL = 5 VDC, RL = 5.1 kΩ | 1.3 | μs | ||

| Output sink current | VIN(−)= 1 VDC, VIN(+) = 0, VO ≤ 1.5 VDC | 6 | 16 | mADC | |

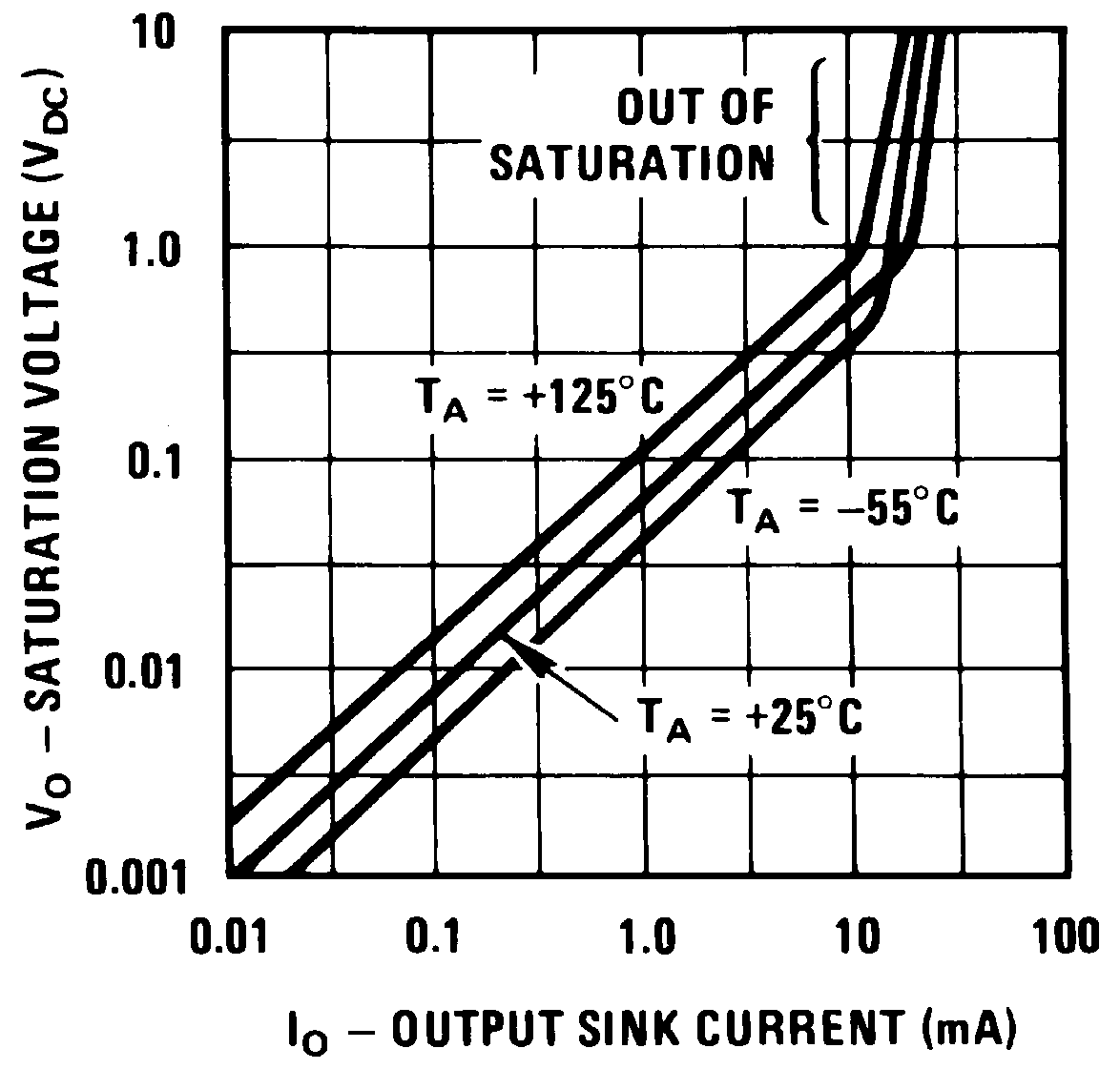

| Saturation voltage | VIN(−) = 1 VDC, VIN(+) = 0, ISINK ≤ 4 mA | 250 | 400 | mVDC | |

| VIN(−) = 1 VDC, VIN(+) = 0, ISINK ≤ 4 mA, 0°C ≤ TA ≤ 70°C |

700 | ||||

| Output leakage current | VIN(+) = 1 VDC,VIN(−) = 0, VO = 5 VDC | 0.1 | nADC | ||

| VIN(+) = 1 VDC, VIN(−) = 0, VO = 30 VDC, 0°C ≤ TA ≤ 70°C |

1 | µADC | |||

| Differential input voltage(4) | Keep all VINs ≥ 0 VDC (or V–, if used), 0°C ≤ TA ≤ 70°C |

36 | VDC |

(1) The direction of the input current is out of the IC due to the PNP input stage. This current is essentially constant, independent of the state of the output so no loading change exists on the reference or input lines.

(2) The input common-mode voltage or either input signal voltage should not be allowed to go negative by more than 0.3 V. The upper end of the common-mode voltage range is V+ −1.5 V at 25°C, but either or both inputs can go to 30 VDC without damage, independent of the magnitude of V+.

(3) The response time specified is a 100-mV input step with 5-mV overdrive. For larger overdrive signals 300 ns can be obtained, see typical performance characteristics section.

(4) Positive excursions of input voltage may exceed the power supply level. As long as the other voltage remains within the common-mode range, the comparator will provide a proper output state. The low input voltage state must not be less than −0.3 VDC (or 0.3 VDCbelow the magnitude of the negative power supply, if used) (at 25°C).

6.6 Typical Characteristics

Positive Transition

Negative Transition