GERY022 December 2024 AMC0106M05 , AMC0106M25 , AMC0136 , AMC0311D , AMC0311S , AMC0386 , AMC0386-Q1 , AMC1100 , AMC1106M05 , AMC1200 , AMC1200-Q1 , AMC1202 , AMC1203 , AMC1204 , AMC1211-Q1 , AMC1300 , AMC1300B-Q1 , AMC1301 , AMC1301-Q1 , AMC1302-Q1 , AMC1303M2510 , AMC1304L25 , AMC1304M25 , AMC1305M25 , AMC1305M25-Q1 , AMC1306M05 , AMC1306M25 , AMC1311 , AMC1311-Q1 , AMC131M03 , AMC1336 , AMC1336-Q1 , AMC1350 , AMC1350-Q1 , AMC23C12 , AMC3301 , AMC3330 , AMC3330-Q1

- 1

- Einführung

- Einführung in die isolierte Signalkette

- Auswahlb?ume

-

Strommessung

- Shunt-Widerstandsauswahl für isolierte Datenwandler

- Designüberlegungen für die isolierte Strommessung

- Isolierte Strommessschaltung mit ±50?mV-Eingang und unsymmetrischem Ausgang

- Isolierte Strommessschaltung mit ±50?mV-Eingang und Differenzausgang

-

Isolierte Strommessschaltung mit ±250?mV Eingangsbereich und unsymmetrischer Ausgangsspannung

- Designziele

- Designbeschreibung

- Designhinweise

- Designschritte

- Design-Simulationen

- DC-Simulationsergebnisse

- Ergebnisse der AC-Simulation im geschlossenen Regelkreis

- Ergebnisse der Transienten-Simulation

- Designreferenzen

- Design empfohlener isolierter Verst?rker

- Design Alternativer Isolierter Verst?rker

- Isolierter Strommessschaltkreis mit ±250?mV-Eingang und Differenzausgang

- Isolierter überstromschutzschaltkreis

- Anschluss eines Differenzialausgangsverst?rkers (isoliert) an einen A/D-Wandler mit unsymmetrischem Eingang

- Verwendung von AMC3311 zur Stromversorgung des AMC23C11 für isolierte Sensorik und Fehlererkennung

- Isolierte Strommessschaltung mit Frontend-Verst?rkungsstufe

- Genauigkeitsvergleich von isolierten Shunt- und Geschlossener Regelkreis-Strommessungen

-

Spannungserfassung

- Maximieren Sie die Leistungswandlung und die Wirksamkeit der Motorsteuerung durch isolierte Spannungserfassung

- H?here Genauigkeit und Leistung mit integrierten isolierten Verst?rkern und Modulatoren mit Hochspannungswiderstand

- Isolierte Verst?rker mit differenziellen, unsymmetrischen Festverst?rkern und ratiometrischen Ausg?ngen für Spannungssensoranwendungen

- Isolierte Spannungsmessschaltung mit ±250?mV-Eingang und Differenzausgang

- Split-Tap-Verbindung für isolierte Line-to-Line-Spannungsmessung mit AMC3330

- ±12 V-Spannungssensorschaltung mit isoliertem Verst?rker und pseudo-differenziellem Eingang SAR-ADC

- ±12 V-Spannungssensorschaltung mit isoliertem Verst?rker und SAR-ADC mit Differenzeingang

- Isolierter Schaltkreis zur Erkennung von Unter- und überspannung

- Isolierter Nulldurchgangsschaltkreis

- Isolierter Spannungssensorschaltkreis mit ±480?V und Differenzausgang

-

EMI-Leistung

-

Beste EMI-Leistung in ihrer Klasse bei Strahlungsemissionen mit isolierten Verst?rkern

- Beste EMI-Leistung in ihrer Klasse bei Strahlungsemissionen mit isolierten Verst?rkern

- Einführung

- Aktuelle Generation von isolierten Verst?rkern von Texas Instruments Strahlungsemissionenleistung

- Frühere Generationen von isolierten Verst?rkern von Texas Instruments strahlen St?rstrahlungsleistung aus

- Fazit

- Quellennachweise

- Bew?hrte Methoden zur D?mpfung von EMI-St?rstrahlungen der AMC3301-Familie

-

Beste EMI-Leistung in ihrer Klasse bei Strahlungsemissionen mit isolierten Verst?rkern

-

Endger?te

- Vergleich von isolierten Shunt- und Hall-basierten Strommessl?sungen in Hybrid- und Elektrofahrzeugen

-

Designüberlegungen für die Strommessung in DC-EV-Ladeanwendungen

- Kurzfassung

- Einführung

-

Strommessung in AC/DC-Wandlern

- Grundlegende Hardware und Steuerungsbeschreibung von AC/DC

- Punkt A und B – AC/DC AC-Phasenstrommessung

- Punkt C und D – AC/DC DC-Link-Strommessung

- Zusammenfassung der positiven und negativen Punkte an den Punkten A, B, C1/2 und D1/2 sowie Produktvorschl?ge

- Strommessung in DC/DC-Wandlern

- Fazit

- Quellennachweise

-

Verwendung isolierter Komparatoren zur Fehlererkennung in Elektromotorantrieben

- Einführung

- Einführung in Elektromotorantriebe

- Verst?ndnis von Fehlerereignissen in Elektromotorantrieben

- Zuverl?ssige Erkennung und Schutz in Elektromotorantrieben

- Anwendungsfall Nr. 1: Bidirektionale Phasenüberstromerkennung

- Anwendungsfall Nr. 2: DC+-überstromerkennung

- Anwendungsfall Nr. 3: DC–überstrom- oder Kurzschlusserkennung

- Anwendungsfall Nr. 4: DC-Link (DC+ zu DC-) überspannungs- und Unterspannungserkennung

- Anwendungsfall Nr. 5: übertemperaturerkennung des IGBT-Moduls

- Diskrete DESAT für optokompatible isolierte Gate-Treiber UCC23513 in Motorantrieben

- Isolierte Spannungserfassung in AC-Motorantrieben

- Hochleistungsf?hige isolierte Strom- und Spannungsmessung in Server-Netzteilen

-

Zus?tzliche Referenzdesigns/Schaltkreise

- Entwicklung einer Bootstrap-Ladepumpen-Stromversorgung für einen isolierten Verst?rker

-

Taktflankenverz?gerungskompensation mit isolierten Modulatoren Digitale Schnittstelle zu MCUs

- Zusammenfassung

- Einführung

- Design-Herausforderung durch Timing-Spezifikationen für digitale Schnittstellen

- Designansatz mit Taktflankenverz?gerungskompensation

- Test und Validierung

- Fazit

- Quellennachweise

- Verwendung von AMC3311 zur Stromversorgung des AMC23C11 für isolierte Sensorik und Fehlererkennung

Bew?hrte Methoden für das Leiterplatten-Layout für mehrere AMC3301

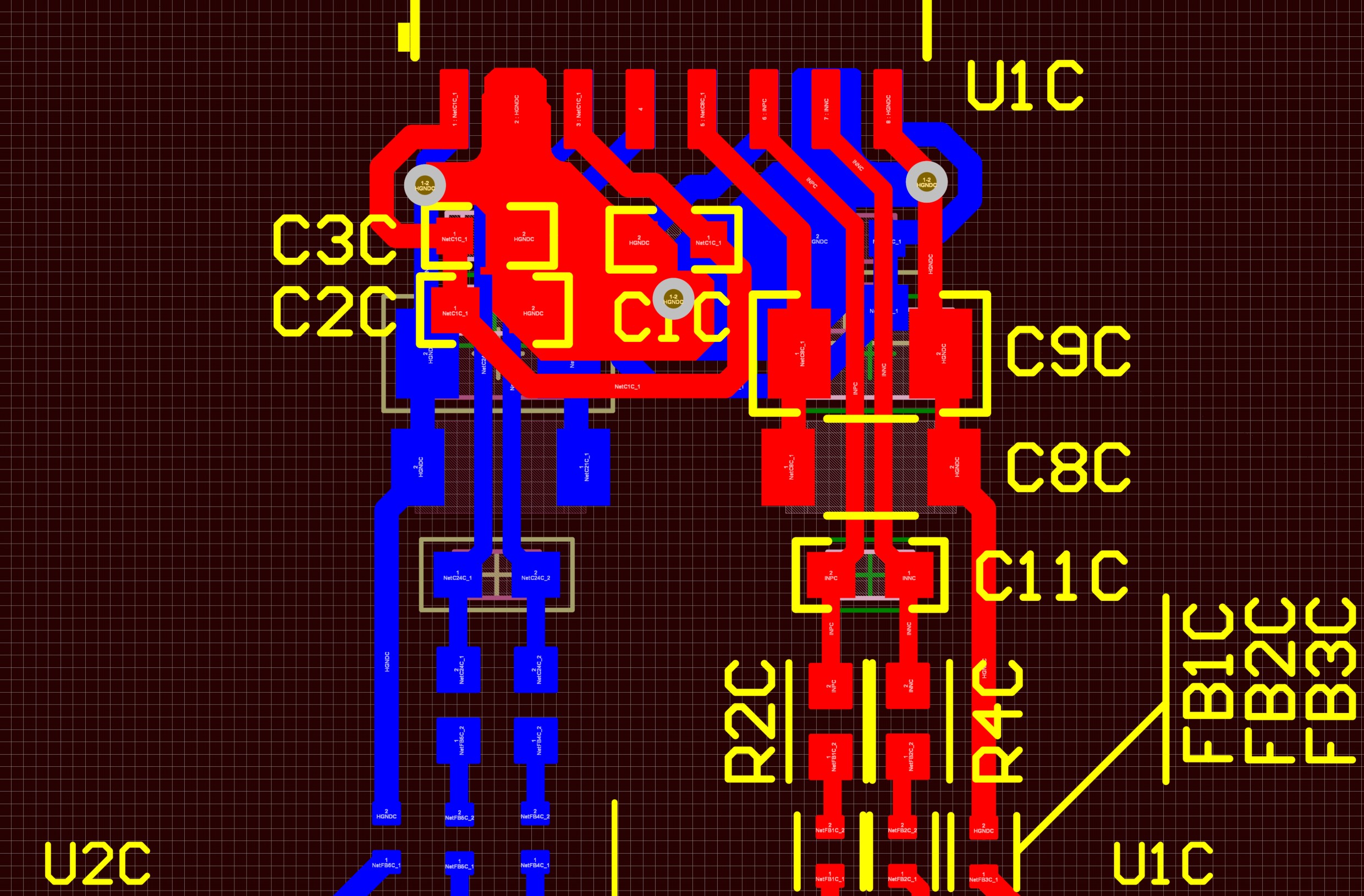

Der bei der Prüfung verwendete Schaltplan ist der gleiche wie der Ferrit-Abschnitt von Abbildung 67. Das Layout zum Stapeln der AMC3301 ist jedoch in Abbildung 67 dargestellt.

Abbildung 67 Empfohlenes Layout für mehrere AMC3301-Bausteine

Abbildung 67 Empfohlenes Layout für mehrere AMC3301-BausteineIm Allgemeinen werden die gleichen in Sektion 6.2.3.2 beschriebenen Layoutprinzipien mit einem zweilagigen Leiterplattendesign befolgt.

Allerdings wird ein direkter und induktivit?tsarmer Pfad von Pin 2 (DCDC_HGND) zu Pin 8 (HGND) jedes Bausteins unterschiedlich erreicht. Anstelle einer Spur verbindet eine Sternverbindung beide Bausteine zwischen der oberen und der unteren Schicht an den Pins 4 und 5. Darüber hinaus wird ein Kupferpool verwendet, um die DC/DC-Kondensatoren mit DCDC_HGND auf derselben Schicht zu verbinden.

Schlie?lich werden die LDO_OUT-Kondensatoren auf ein 1206-Geh?use skaliert, um einen direkten und unterbrechungsfreien Pfad für die positiven und negativen Eing?nge unter den Kondensatoren zu erm?glichen.