ZHCSI14A April 2018 – January 2022 LMK00334-Q1

PRODUCTION DATA

- 1 特性

- 2 應(yīng)用

- 3 說明

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

封裝選項(xiàng)

機(jī)械數(shù)據(jù) (封裝 | 引腳)

- RTV|32

散熱焊盤機(jī)械數(shù)據(jù) (封裝 | 引腳)

- RTV|32

訂購信息

6.7 Typical Characteristics

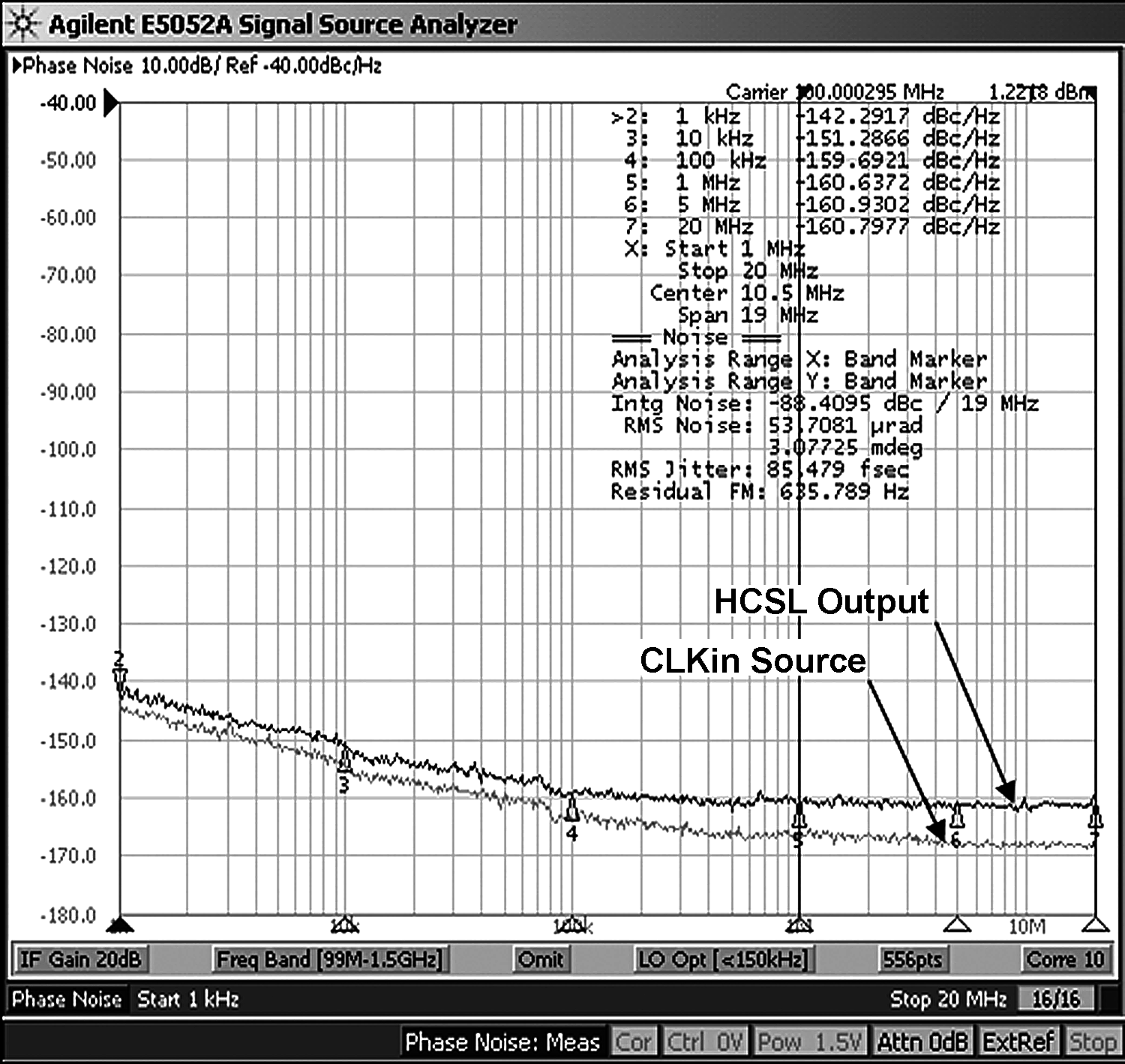

Unless otherwise specified: VCC = 3.3 V, VCCO = 3.3 V, TA = 25°C, CLKin driven differentially, input slew rate ≥ 3 V/ns.

Figure 6-1 HCSL

Output Swing at 250 MHz

Figure 6-1 HCSL

Output Swing at 250 MHz

| Fclk = 100 MHz | Foffset = 20 MHz |

| Fclk = 100 MHz | Int. BW = 1 to 20 MHz | |

| Fclk = 156.25 MHz | Vccco Ripple = 100 mVpp | |

Figure 6-9 Propagation Delay vs. Temperature

Figure 6-9 Propagation Delay vs. Temperature Figure 6-11 HCSL

Phase Noise at 100 MHz

Figure 6-11 HCSL

Phase Noise at 100 MHz Figure 6-2 LVCMOS Output Swing at 250 MHz

Figure 6-2 LVCMOS Output Swing at 250 MHz

| Fclk = 156.25 MHz | Foffset = 20 MHz |

| Fclk = 156.25 MHz | Int. BW = 1 to 20 MHz | |

| Fclk = 312.5 MHz | Vccco Ripple = 100 mVpp | |

Figure 6-10 Crystal Power Dissipation vs. RLIM

Figure 6-10 Crystal Power Dissipation vs. RLIM