SNLS020D July 1999 – August 2016 DS90LV031A

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

封裝選項(xiàng)

機(jī)械數(shù)據(jù) (封裝 | 引腳)

散熱焊盤機(jī)械數(shù)據(jù) (封裝 | 引腳)

訂購信息

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| Supply voltage, VCC | –0.3 | 4 | V | |

| Input voltage, DIN | –0.3 | VCC + 0.3 | V | |

| Enable input voltage, EN, EN* | –0.3 | VCC + 0.3 | V | |

| Output voltage, DOUT+, DOUT− | –0.3 | 3.9 | V | |

| Short circuit duration, DOUT+, DOUT− | Continuous | |||

| Lead temperature, soldering (4 s) | 260 | °C | ||

| Maximum junction temperature | 150 | °C | ||

| Storage temperature, Tstg | –65 | 150 | °C | |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

6.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | ±6000 | V |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions.

6.3 Recommended Operating Conditions

| MIN | NOM | MAX | UNIT | |||

|---|---|---|---|---|---|---|

| VCC | Supply voltage | 3 | 3.3 | 3.6 | V | |

| TA | Operating free-air temperature, industrial | –40 | 25 | 85 | °C | |

6.4 Thermal Information

| THERMAL METRIC(1) | DS90LV031A | UNIT | ||

|---|---|---|---|---|

| PW (TSSOP) | D (SOIC) | |||

| 16 PINS | 16 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 114 | 75 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 51 | 36 | °C/W |

| RθJB | Junction-to-board thermal resistance | 59 | 32 | °C/W |

| ψJT | Junction-to-top characterization parameter | 8 | 6 | °C/W |

| ψJB | Junction-to-board characterization parameter | 58 | 31.7 | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

6.5 Electrical Characteristics

over supply voltage and operating temperature ranges (unless otherwise noted)(1)(2)(3)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| VOD1 | Differential output voltage | RL = 100 Ω, DOUT−, DOUT+ pins (see Figure 3) | 250 | 350 | 450 | mV |

| ΔVOD1 | Change in magnitude of VOD1

for complementary output states |

RL = 100 Ω, DOUT−, DOUT+ pins (see Figure 3) | 4 | 35 | |mV| | |

| VOS | Offset voltage | RL = 100 Ω, DOUT−, DOUT+ pins (see Figure 3) | 1.125 | 1.25 | 1.375 | V |

| ΔVOS | Change in magnitude of VOS

for complementary output states |

RL = 100 Ω, DOUT−, DOUT+ pins (see Figure 3) | 5 | 25 | |mV| | |

| VOH | Output voltage high | RL = 100 Ω, DOUT−, DOUT+ pins (see Figure 3) | 1.38 | 1.6 | V | |

| VOL | Output voltage low | RL = 100 Ω, DOUT−, DOUT+ pins (see Figure 3) | 0.90 | 1.03 | V | |

| VIH | Input voltage high | DIN, EN, EN* pins | 2 | VCC | V | |

| VIL | Input voltage low | DIN, EN, EN* pins | GND | 0.8 | V | |

| IIH | Input current high | VIN = VCC or 2.5 V, DIN, EN, EN* pins | −10 | ±1 | 10 | µA |

| IIL | Input current low | VIN = GND or 0.4 V, DIN, EN, EN* pins | −10 | ±1 | 10 | µA |

| VCL | Input clamp voltage | ICL = –18 mA, DIN, EN, EN* pins | −1.5 | −0.8 | V | |

| IOS | Output short circuit current | Enabled, DOUT−, DOUT+ pins(4), DIN = VCC, DOUT+ = 0 V, or DIN = GND, DOUT− = 0 V | −6 | −9 | mA | |

| IOSD | Differential output short circuit current | Enabled, VOD = 0 V, DOUT−, DOUT+ pins(4) | −6 | −9 | mA | |

| IOFF | Power-off leakage | VOUT = 0 V or 3.6 V, VCC = 0 V or open, DOUT−, DOUT+ pins | −20 | ±1 | 20 | µA |

| IOZ | Output TRI-STATE current | EN = 0.8 V and EN* = 2 V, VOUT = 0 V or VCC, DOUT−, DOUT+ pins | −10 | ±1 | 10 | µA |

| ICC | No load supply current drivers enabled | DIN = VCC or GND, VCC pin | 5 | 8 | mA | |

| ICCL | Loaded supply current drivers enabled | RL = 100 Ω (all channels), DIN = VCC or GND (all inputs), VCC pin | 23 | 30 | mA | |

| ICCZ | No load supply current drivers disabled | DIN = VCC or GND, EN = GND, EN* = VCC, VCC pin | 2.6 | 6 | mA | |

(1) Current into device pins is defined as positive. Current out of device pins is defined as negative. All voltages are referenced to ground except: VOD1 and ΔVOD1.

(2) All typicals are given for: VCC = 3.3 V, TA = 25°C.

(3) The DS90LV031A is a current mode device and only functions within datasheet specifications when a resistive load is applied to the driver outputs typical range is (90 Ω to 110 Ω)

(4) Output short-circuit current (IOS) is specified as magnitude only, minus sign indicates direction only.

6.6 Switching Characteristics – Industrial

VCC = 3.3 V ±10% and TA = –40°C to 85°C (unless otherwise noted)(1)(2)(3)| MIN | NOM | MAX | UNIT | |||

|---|---|---|---|---|---|---|

| tPHLD | Differential propagation delay high to low |

RL = 100 Ω and CL = 10 pF (see Figure 4 and Figure 5) | 0.8 | 1.18 | 2 | ns |

| tPLHD | Differential propagation delay low to high |

RL = 100 Ω and CL = 10 pF (see Figure 4 and Figure 5) | 0.8 | 1.25 | 2 | ns |

| tSKD1 | Differential pulse skew(4)

|tPHLD − tPLHD| |

RL = 100 Ω and CL = 10 pF (see Figure 4 and Figure 5) | 0 | 0.07 | 0.4 | ns |

| tSKD2 | Channel-to-channel skew(5) | RL = 100 Ω and CL = 10 pF (see Figure 4 and Figure 5) | 0 | 0.1 | 0.5 | ns |

| tSKD3 | Differential part-to-part skew(6) | RL = 100 Ω and CL = 10 pF (see Figure 4 and Figure 5) | 0 | 1 | ns | |

| tSKD4 | Differential part-to-part skew(7) | RL = 100 Ω and CL = 10 pF (see Figure 4 and Figure 5) | 0 | 1.2 | ns | |

| tTLH | Rise time | RL = 100 Ω and CL = 10 pF (see Figure 4 and Figure 5) | 0.38 | 1.5 | ns | |

| tTHL | Fall time | RL = 100 Ω and CL = 10 pF (see Figure 4 and Figure 5) | 0.4 | 1.5 | ns | |

| tPHZ | Disable time high to Z | RL = 100 Ω and CL = 10 pF (see Figure 6 and Figure 7) | 5 | ns | ||

| tPLZ | Disable time low to Z | RL = 100 Ω and CL = 10 pF (see Figure 6 and Figure 7) | 5 | ns | ||

| tPZH | Enable time Z to high | RL = 100 Ω and CL = 10 pF (see Figure 6 and Figure 7) | 7 | ns | ||

| tPZL | Enable time Z to low | RL = 100 Ω and CL = 10 pF (see Figure 6 and Figure 7) | 7 | ns | ||

| fMAX | Maximum operating frequency(8) | 200 | 250 | MHz | ||

(1) All typicals are given for: VCC = 3.3 V, TA = 25°C.

(2) Generator waveform for all tests unless otherwise specified: f = 1 MHz, ZO = 50 Ω, tr ≤ 1 ns, and tf ≤ 1 ns.

(3) CL includes probe and jig capacitance.

(4) tSKD1, |tPHLD − tPLHD| is the magnitude difference in differential propagation delay time between the positive going edge and the negative going edge of the same channel.

(5) tSKD2 is the differential channel-to-channel skew of any event on the same device.

(6) tSKD3, differential part-to-part skew, is defined as the difference between the minimum and maximum specified differential propagation delays. This specification applies to devices at the same VCC and within 5°C of each other within the operating temperature range.

(7) tSKD4, part-to-part skew, is the differential channel-to-channel skew of any event between devices. This specification applies to devices over recommended operating temperature and voltage ranges, and across process distribution. tSKD4 is defined as |Max − Min| differential propagation delay.

(8) fMAX generator input conditions: tr = tf < 1 ns, (0% to 100%), 50% duty cycle, 0 V to 3 V. Output criteria: duty cycle = 45% / 55%, VOD > 250 mV, all channels switching.

6.7 Dissipation Ratings

| MAXIMUM PACKAGE POWER DISSIPATION AT 25°C | |

|---|---|

| D package | 1088 mW |

| PW package | 866 mW |

| Derate D package | 8.5 mW/°C above 25°C |

| Derate PW package | 6.9 mW/°C above 25°C |

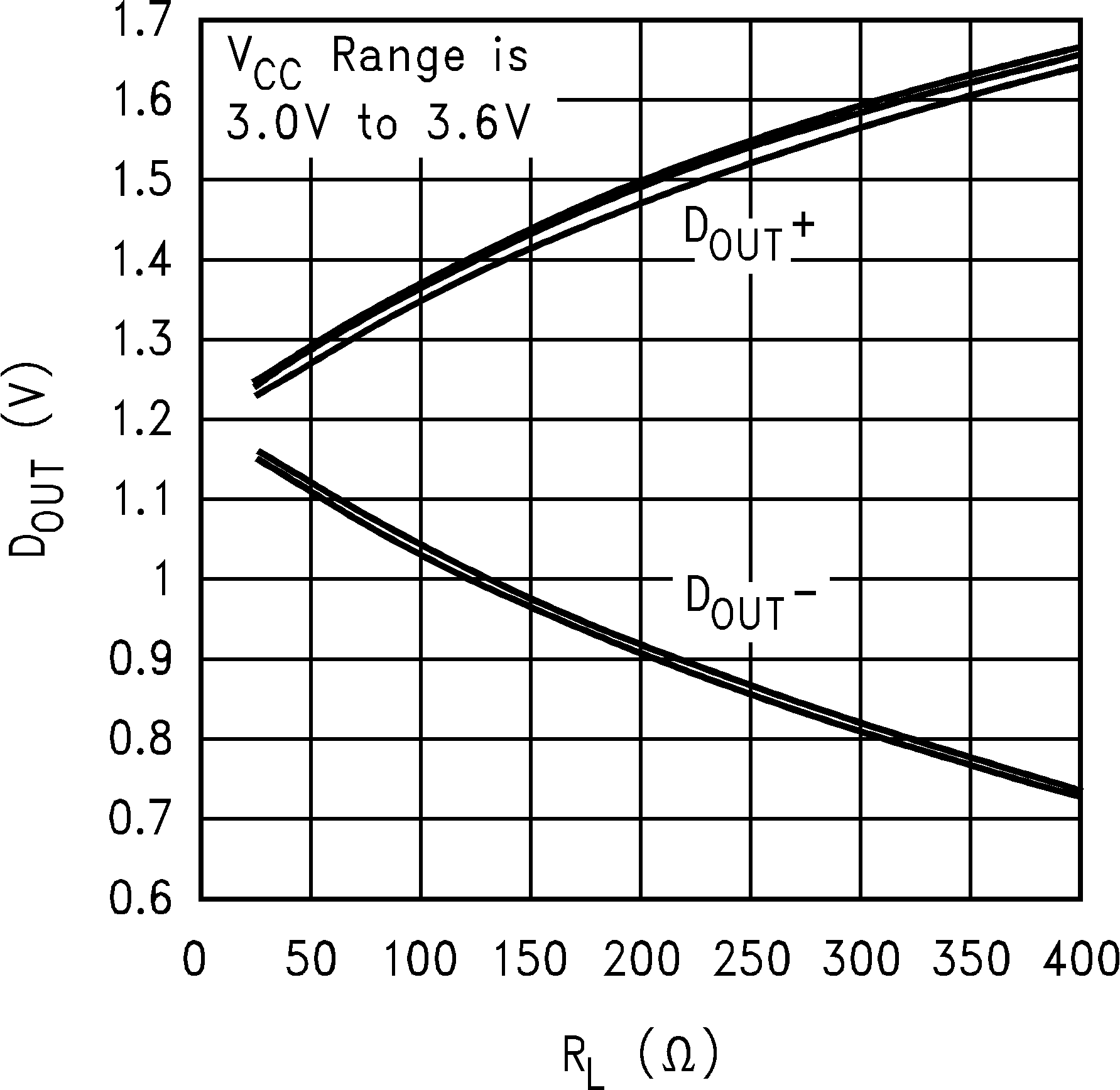

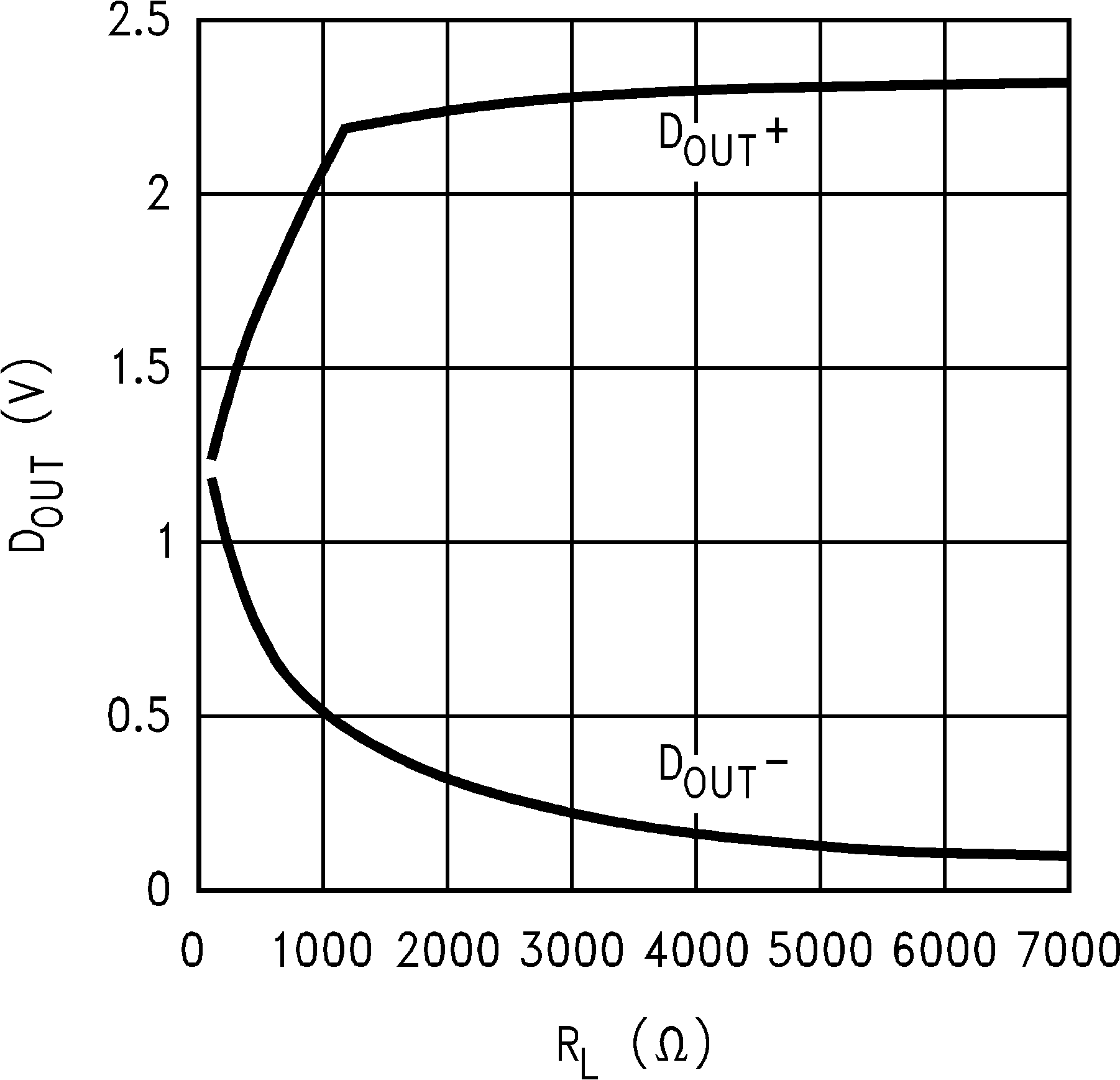

6.8 Typical Characteristics

Figure 1. Typical DS90LV031A, DOUT (Single-Ended)

Figure 1. Typical DS90LV031A, DOUT (Single-Ended)vs RL, TA = 25°C

Figure 2. Typical DS90LV031A, DOUT

Figure 2. Typical DS90LV031A, DOUT

vs RL, VCC = 3.3 V, TA = 25°C